Нод конструирование из бумаги в старшей группе: Конструирование из бумаги в старшей группе «Собачка» | План-конспект занятия по конструированию, ручному труду (старшая группа):

| Конспект НОД с участием родителей в средней группе. Конструированию из бумаги «Босоножки» Цель: обучать конструированию из бумаги. Задачи:

Оборудование: коробка – посылка почтовая, босоножки из бумаги – образец, ножницы, клей, салфетки по количеству детей и взрослых, картон (прямоугольник с нарисованным контуром следа обуви 16. 5см. х8см. — подошва) и цветная бумага (полоска 15см. х4 см. и полоска 30см. х2см. – ремешки для босоножек) по количеству детей и взрослых (цвет картона совпадает с цветом цветной бумаги), украшения для ремешков из цветной бумаги (кружочки, сердечки и др.) Ход НОД:

Ставят ловких две руки. Каблучки на башмачки, И набойки на каблук – Тоже дело этих рук. (сапожник) — Что делает сапожник? Воспитатель заглядывает в посылку — Дети, в посылки лежит обувь, какую обувь вы знаете? Воспитатель достает из посылки босоножки. — Как называется эта обувь, почему? Воспитатель читает письмо от сапожника. «Пожалуйста, помогите выполнить большой заказ по изготовлению босоножек. Присылаю вам детали: подошвы и ремешки. Их нужно подготовить и склеить. Заранее спасибо. Сапожник» 3. Воспитатель достает из посылки прямоугольники из картона. Игра «Найди пару». Детям раздаются по одному прямоугольнику (с контуром следа). На стол выкладываются остальные. Детям нужно подобрать соответствующую по цвету левую или правую пару обуви. 4. Воспитатель достает из посылки полоски из цветной бумаги, выкладывает на стол. Игра «Подбери по цвету» Детям нужно подобрать к подошве соответствующие по цвету ремешки (широкую и узкую полоску). 5. Физминутка «Вот правая, вот левая» (песенка на слова и музыку Екатерины и Сергея Железновых). Воспитатель, родители и дети выполняют действия в соответствии с текстом песенки. 6. Взрослые и дети присаживаются за столы. Воспитатель показывает способ изготовления босоножек из деталей и объясняет, кто, что будет делать. Родители вырезают из картона подошву по контуру. Дети: — складывают широкую полоску пополам (длинная сторона к длинной стороне), проглаживают сгиб, разворачивают и разрезают полоску на две части по линии сгиба. — складывают узкую полоску пополам (короткая сторона к короткой стороне) проглаживают сгиб, разворачивают и разрезают полоску на две части по линии сгиба. Родители и дети вместе приклеивают на узкие полоски украшения, потом приклеивают ремешки к подошве (узкую полоску на носок, а широкую полоску под углом на пяточку). 7. Воспитатель беседует с детьми о правилах работы с ножницами. — Не держать ножницы концами вверх. — Не оставлять ножницы в открытом виде. — При работе следить за пальцами левой руки. — Класть ножницы на стол так, чтобы они не свешивались за край стола. — Передавать ножницы в закрытом виде кольцами в сторону товарища. — Не резать ножницами на ходу, не подходить к товарищу во время резания. 8. Воспитатель проводит с детьми и родителями пальчиковую гимнастику. Пять пальцев на руке своей Назвать по имени сумей. Первый палец – боковой- Называется большой. Палец второй – Указчик старательный, Не зря называют его Указательный. Третий твой палец – Как раз по средине. Поэтому средний Дано ему имя. Палец четвертый Зовут безымянный, Неповоротливый он И упрямый. Совсем как в семье, Братец младший – любимец. По счету он пятый, Зовется мизинец. 9. Дети и родители приступают к изготовлению босоножек. 10. Итог. Выставка босоножек. Список используемой литературы: Дошкольный логопункт. Раздаточный материал для работы с детьми 5-7 лет.

|

Копия Сертификат-новыйДошкольник. ru ru

ПедагогамПраздникиРукоделиеДошкольник.руДошкольник.ру – сайт воспитателя, логопеда, дефектолога, музыкального руководителя, методиста, инструктора по физической культуре, родителя. Предлагаем педагогам помощь в аттестации. СервисыРазмещаем статьи

|

|

Журнал“Дошкольник. РФ” РФ”

|

|||||||||||

Chip Design with Deep Reinforcement Learning — блог Google AI

Авторы: Анна Голди, старший инженер-программист, и Азалия Мирхосейни, старший научный сотрудник, Google Research, Brain Team

Обновление, 9 июня 2021 г.: Сегодня в природе мы опубликовали методы, которые улучшают то, что обсуждается ниже, и которые использовались в производстве для разработки следующего поколения TPU Google.

Революция в области современных вычислений во многом стала возможной благодаря выдающимся достижениям в области компьютерных систем и аппаратного обеспечения. С замедлением действия закона Мура и масштабирования Деннарда мир движется к специализированному оборудованию, чтобы удовлетворить экспоненциально растущий спрос на вычисления. Однако на разработку современных чипов уходят годы, что приводит к необходимости размышлять о том, как оптимизировать чипы следующего поколения для моделей машинного обучения (ML) через 2–5 лет.

В «Размещение чипов с помощью глубокого обучения с подкреплением» мы представляем размещение чипов как проблему обучения с подкреплением (RL), где мы обучаем агента (то есть политику RL) для оптимизации качества размещения чипов. В отличие от предыдущих методов, наш подход позволяет учиться на прошлом опыте и со временем совершенствоваться. В частности, по мере того, как мы тренируемся на большем количестве блоков микросхем, наш метод становится лучше для быстрого создания оптимизированных мест размещения ранее невидимых блоков микросхем. В то время как для существующих базовых показателей требуются специалисты-люди, а их создание занимает несколько недель, наш метод может генерировать места размещения менее чем за шесть часов, которые превосходят или соответствуют своим аналогам, разработанным вручную.

Проблема планирования этажа чипа

Компьютерный чип разделен на десятки блоков, каждый из которых представляет собой отдельный модуль, например, подсистему памяти, вычислительный блок или систему управляющей логики. Эти блоки могут быть описаны с помощью списка соединений

, графа компонентов схемы, таких как макросы (компоненты памяти) и стандартных ячеек (логические элементы, такие как NAND, NOR и XOR), все из которых соединены проводами. . Определение компоновки блока микросхемы, процесс, называемый планировкой микросхемы, является одним из наиболее сложных и трудоемких этапов процесса проектирования микросхемы и включает в себя размещение списка соединений на холсте микросхемы (двухмерную сетку), чтобы мощность, производительность , и площадь (PPA) сведены к минимуму при соблюдении ограничений по плотности и перегрузке маршрутизации. Несмотря на десятилетия исследований по этой теме, специалистам по-прежнему необходимо неделями проводить итерации для создания решений, отвечающих многогранным критериям проектирования. Сложность этой проблемы возникает из-за размера графа списка соединений (от миллионов до миллиардов узлов), гранулярности сетки, на которую должен быть помещен этот граф, и непомерной стоимости вычисления истинных целевых показателей, которые могут занять много часов (иногда в течение дня) с использованием стандартных инструментов автоматизации электронного проектирования.

Несмотря на десятилетия исследований по этой теме, специалистам по-прежнему необходимо неделями проводить итерации для создания решений, отвечающих многогранным критериям проектирования. Сложность этой проблемы возникает из-за размера графа списка соединений (от миллионов до миллиардов узлов), гранулярности сетки, на которую должен быть помещен этот граф, и непомерной стоимости вычисления истинных целевых показателей, которые могут занять много часов (иногда в течение дня) с использованием стандартных инструментов автоматизации электронного проектирования.

Модель глубокого обучения с подкреплением

Входными данными для нашей модели является список соединений микросхемы (типы узлов и информация о смежности графа), идентификатор текущего узла, который необходимо разместить, и некоторые метаданные списка соединений, такие как общее количество проводов. , макросы и стандартные кластеры ячеек. Граф списка соединений и текущий узел передаются через нейронную сеть графа на основе ребер, которую мы разработали для кодирования входного состояния. Это генерирует вложения частично размещенного графа и узла-кандидата.

Это генерирует вложения частично размещенного графа и узла-кандидата.

| Нейронная сеть графа генерирует вложения, которые объединяются с вложениями метаданных, чтобы сформировать входные данные для политики и сетей ценности. |

Затем встраивания метаданных ребер, макросов и списка соединений объединяются для формирования встраивания одного состояния, которое передается в нейронную сеть с прямой связью. Результатом сети прямой связи является изученное представление, которое фиксирует полезные функции и служит входными данными для политик и сетей создания стоимости. Сеть политик генерирует распределение вероятностей по всем возможным ячейкам сетки, на которые может быть помещен текущий узел.

В каждой итерации обучения макросы последовательно размещаются агентом RL, после чего стандартные кластеры ячеек размещаются силовым методом, который моделирует схему как систему пружин для минимизации длины провода.

| Во время каждой обучающей итерации макросы размещаются политикой по одному, а стандартные кластеры ячеек размещаются принудительно направленным методом. Вознаграждение рассчитывается на основе взвешенной комбинации приблизительной длины провода и перегрузки. |

Результаты

Насколько нам известно, этот метод является первым подходом к размещению микросхем, который имеет возможность обобщать, а это означает, что он может использовать то, что он узнал при размещении предыдущих списков соединений, для создания лучших мест для новых невидимых списков соединений. Мы показываем, что по мере увеличения числа списков соединений микросхем, на которых мы проводим предварительное обучение (т. е. по мере того, как наш метод становится более опытным в оптимизации размещения), наша политика лучше обобщается на новые списки соединений.

е. по мере того, как наш метод становится более опытным в оптимизации размещения), наша политика лучше обобщается на новые списки соединений.

Например, предварительно обученная политика органично идентифицирует расположение, при котором макросы размещаются у краев чипа с выпуклым пространством в центре, в котором размещаются стандартные ячейки. Это приводит к меньшей длине провода между макросами и стандартными ячейками без чрезмерной перегрузки маршрутизации. Напротив, политика, обученная с нуля, начинается со случайного размещения и требует гораздо больше времени, чтобы прийти к высококачественному решению, заново обнаруживая необходимость оставлять отверстие в центре холста чипа. Это показано на анимации ниже.

Размещение макросов Ariane, процессора RISC-V с открытым исходным кодом, по мере обучения. Слева политика обучается с нуля, а справа предварительно обученная политика дорабатывается под этот чип. Каждый прямоугольник представляет отдельное размещение макроса. Обратите внимание, что полость, обнаруженная политикой с нуля, уже присутствует с самого начала в размещении предварительно обученной политики. Каждый прямоугольник представляет отдельное размещение макроса. Обратите внимание, что полость, обнаруженная политикой с нуля, уже присутствует с самого начала в размещении предварительно обученной политики. |

Мы наблюдаем, что предварительное обучение повышает эффективность выборки и качество размещения. Мы сравниваем качество мест размещения, созданных с использованием предварительно обученных политик, с теми, которые были созданы путем обучения политики с нуля. Чтобы сгенерировать размещение для ранее невиданных блоков микросхем, мы используем метод с нулевым выстрелом , что означает, что мы просто используем предварительно обученную политику (без точной настройки) для размещения нового блока, что дает размещение менее чем за секунду. . Результаты могут быть дополнительно улучшены путем точной настройки политики на новом блоке. Политика, обученная с нуля, требует гораздо больше времени для сходимости, и даже через 24 часа ее размещение чипов хуже, чем то, что достигается с помощью точно настроенной политики через 12 часов.

| Графики конвергенции для двух политик на блоках Ariane. Один занимается обучением с нуля, а другой — тонкой настройкой предварительно обученной политики. |

Производительность нашего подхода улучшается по мере того, как мы тренируемся на большем наборе данных. Мы заметили, что по мере того, как мы увеличиваем тренировочный набор с двух блоков до пяти, а затем до 20 блоков, политика обеспечивает лучшее размещение как при нулевом выстреле, так и после точной настройки для одного и того же времени обучения на настенных часах.

| Размер обучающих данных и производительность тонкой настройки. |

Способность нашего подхода учиться на собственном опыте и со временем совершенствоваться открывает новые возможности для разработчиков микросхем. Поскольку агент подвергается воздействию большего объема и разнообразия чипов, он становится быстрее и лучше в создании оптимизированных мест размещения для новых блоков чипов. Быстрый, высококачественный, автоматический метод размещения чипов может значительно ускорить проектирование чипов и обеспечить совместную оптимизацию с более ранними этапами процесса проектирования чипов. Хотя мы оцениваем в первую очередь микросхемы ускорителей, предлагаемый нами метод широко применим к любой проблеме размещения микросхем. После всего, что аппаратное обеспечение сделало для машинного обучения, мы считаем, что машинному обучению пора вернуть должок.

Поскольку агент подвергается воздействию большего объема и разнообразия чипов, он становится быстрее и лучше в создании оптимизированных мест размещения для новых блоков чипов. Быстрый, высококачественный, автоматический метод размещения чипов может значительно ускорить проектирование чипов и обеспечить совместную оптимизацию с более ранними этапами процесса проектирования чипов. Хотя мы оцениваем в первую очередь микросхемы ускорителей, предлагаемый нами метод широко применим к любой проблеме размещения микросхем. После всего, что аппаратное обеспечение сделало для машинного обучения, мы считаем, что машинному обучению пора вернуть должок.

Благодарности

Этот проект был совместным проектом Google Research и Google Hardware and Architecture. Мы хотели бы поблагодарить наших соавторов: Мустафу Язгана, Джо Цзяна, Эбрахима Сонгхори, Шен Вана, Ён-Джун Ли, Эрика Джонсона, Омкара Патхака, Сунгмин Бэ, Азаде Нази, Джиу Пак, Энди Тонга, Кавью Сриниваса, Уильяма Ханга, Эмре. Tuncer, Anand Babu, Quoc Le, James Laudon, Roger Carpenter, Richard Ho и Jeff Dean за их поддержку и вклад в эту работу.

Tuncer, Anand Babu, Quoc Le, James Laudon, Roger Carpenter, Richard Ho и Jeff Dean за их поддержку и вклад в эту работу.

Проектирование арифметических схем с помощью глубокого обучения с подкреплением

По мере замедления действия закона Мура становится все более важной разработка других методов, улучшающих производительность микросхемы на том же узле технологического процесса. Наш подход использует ИИ для разработки меньших, более быстрых и более эффективных схем, чтобы обеспечить более высокую производительность с каждым поколением чипов.

Огромные массивы арифметических схем позволили графическим процессорам NVIDIA добиться беспрецедентного ускорения для ИИ, высокопроизводительных вычислений и компьютерной графики. Таким образом, улучшение конструкции этих арифметических схем будет иметь решающее значение для повышения производительности и эффективности графических процессоров.

Что, если бы ИИ научился проектировать эти схемы? В PrefixRL: оптимизация параллельных префиксных схем с использованием глубокого обучения с подкреплением мы демонстрируем, что ИИ не только может научиться проектировать эти схемы с нуля, но и схемы, разработанные ИИ, меньше и быстрее, чем схемы, разработанные современными электронными технологиями. средства автоматизации проектирования (EDA). Новейшая архитектура графического процессора NVIDIA Hopper содержит почти 13 000 экземпляров схем, разработанных искусственным интеллектом.

средства автоматизации проектирования (EDA). Новейшая архитектура графического процессора NVIDIA Hopper содержит почти 13 000 экземпляров схем, разработанных искусственным интеллектом.

На рис. 1 схема соответствует точке (31,4 мкм², 0,186 нс) на кривой PrefixRL на рис. 5. NAND, NOR и XOR) и провода. Желаемая схема должна иметь следующие характеристики:

- Небольшой: Меньшая площадь, чтобы на микросхеме могло поместиться больше схем.

- Быстрый: Меньшая задержка для повышения производительности чипа.

- Потребляйте меньше энергии: Более низкое энергопотребление чипа.

В нашей статье мы сосредоточимся на площади цепи и задержке. Мы обнаружили, что потребляемая мощность хорошо коррелирует с площадью интересующих нас цепей. Площадь цепи и задержка часто являются конкурирующими свойствами, поэтому мы хотим найти границу Парето для схем, которая эффективно сочетает эти свойства. Проще говоря, нам нужна схема минимальной площади при каждой задержке.

Площадь цепи и задержка часто являются конкурирующими свойствами, поэтому мы хотим найти границу Парето для схем, которая эффективно сочетает эти свойства. Проще говоря, нам нужна схема минимальной площади при каждой задержке.

В PrefixRL мы фокусируемся на популярном классе арифметических схем, называемых (параллельными) префиксными схемами. Различные важные схемы в графическом процессоре, такие как сумматоры, инкрементаторы и кодировщики, являются префиксными схемами, которые могут быть определены на более высоком уровне как графы префиксов. 9n) и не могут быть исследованы методом полного перебора.

Рис. 2. Одна итерация PrefixRL с примером схемы 4b Граф префикса преобразуется в схему с проводами и логическими вентилями с помощью генератора схем. Эти сгенерированные схемы затем дополнительно оптимизируются с помощью инструмента физического синтеза с использованием оптимизаций физического синтеза, таких как размер вентиля, дублирование и вставка буфера.

Окончательные свойства схемы (задержка, площадь и мощность) не переводятся напрямую из исходных свойств префиксного графа, таких как уровень и количество узлов, из-за этих оптимизаций физического синтеза. Вот почему агент ИИ учится проектировать графы префиксов, но оптимизирует свойства конечной схемы, сгенерированной из графа префиксов.

Мы рассматриваем проектирование арифметических схем как задачу обучения с подкреплением (RL), где мы обучаем агента оптимизировать площадь и свойства задержки арифметических схем. Для схем префиксов мы разрабатываем среду, в которой агент RL может добавлять или удалять узлы из графа префиксов, после чего выполняются следующие шаги:

- Граф префиксов узаконен, чтобы всегда поддерживать правильное вычисление суммы префиксов.

- Цепь генерируется из узаконенного графа префиксов.

- Схема подвергается оптимизации физического синтеза с использованием инструмента физического синтеза.

- Измеряются площадь и задержка цепи.

Во время эпизода агент RL шаг за шагом строит граф префиксов, добавляя или удаляя узлы. На каждом шаге агент получает в качестве вознаграждения улучшение в соответствующей области цепи и задержку.

Представление состояний и действий и модель глубокого обучения с подкреплением

Мы используем алгоритм Q-обучения для обучения агента схемотехники. Мы используем сеточное представление для префиксных графов, где каждый элемент в сетке однозначно соответствует префиксному узлу. Это представление сетки используется как на входе, так и на выходе Q-сети. Каждый элемент во входной сетке представляет, присутствует ли узел или отсутствует. Каждый элемент в выходной сетке представляет Q-значения для добавления или удаления узла.

Мы используем архитектуру полностью сверточной нейронной сети для агента, поскольку вход и выход агента Q-обучения представляют собой сетки. Агент отдельно прогнозирует значения Q для свойств площади и задержки, потому что вознаграждение за площадь и задержку можно наблюдать отдельно во время обучения.

Распределенное обучение с Raptor

PrefixRL требует больших вычислительных ресурсов: для физического моделирования требовалось 256 ЦП для каждого графического процессора, а обучение случая 64b заняло более 32 000 часов графического процессора.

Мы разработали Raptor, собственную распределенную платформу обучения с подкреплением, которая использует преимущества оборудования NVIDIA для такого рода промышленного обучения с подкреплением (рис. 4).

Raptor имеет несколько функций, повышающих масштабируемость и скорость обучения, таких как планирование заданий, настраиваемые сети и структуры данных с поддержкой графического процессора. В контексте PrefixRL Raptor позволяет распределять работу между процессорами, графическими процессорами и спотовыми инстансами.

Сеть в этом приложении обучения с подкреплением разнообразна и имеет следующие преимущества.

- Способность Raptor переключаться между NCCL для двухточечной передачи для передачи параметров модели непосредственно с обучаемого графического процессора на логический графический процессор.

- Redis для асинхронных и небольших сообщений, таких как вознаграждения или статистика.

- RPC, скомпилированный JIT, для обработки больших объемов запросов с малой задержкой, таких как загрузка данных об опыте.

Наконец, Raptor предоставляет структуры данных с поддержкой графического процессора, такие как буфер воспроизведения, который имеет многопоточный сервер для получения опыта от нескольких работников, а также параллельно группирует данные и предварительно загружает их на графический процессор.

На рис. 4 показано, что наша структура обеспечивает параллельное обучение и сбор данных, а также использует преимущества NCCL для эффективной отправки субъектам последних параметров.

Рисунок 4. Мы используем Raptor для несвязанного и параллельного обучения и расчета вознаграждения для преодоления задержки синтеза схемы Мы обучаем различных агентов с различными весами, чтобы получить границу Парето планов, которые уравновешивают компромисс между площадью и задержкой.

Оптимизация физического синтеза в среде RL может генерировать различные решения для компромисса между площадью и задержкой. Мы должны управлять инструментом физического синтеза с тем же компромиссным весом, для которого обучен конкретный агент.

Выполнение оптимизации физического синтеза в цикле вычисления вознаграждения имеет несколько преимуществ.

- Агент RL учится напрямую оптимизировать конечные свойства схемы для целевого технологического узла и библиотеки.

- Агент RL может совместно оптимизировать свойства целевой арифметической схемы и окружающей ее логики путем включения окружающей логики во время физического синтеза.

Однако выполнение физического синтеза — медленный процесс (~35 секунд для сумматоров 64b), что может значительно замедлить обучение и исследование RL.

Мы отделяем вычисление вознаграждения от обновления состояния, поскольку агенту для выполнения действий требуется только текущее состояние графа префикса, а не синтез схемы или предыдущие вознаграждения. Благодаря Raptor мы можем переложить длительный расчет вознаграждения на пул рабочих ЦП для параллельного выполнения физического синтеза, в то время как агенты-акторы проходят через среду без необходимости ждать.

Благодаря Raptor мы можем переложить длительный расчет вознаграждения на пул рабочих ЦП для параллельного выполнения физического синтеза, в то время как агенты-акторы проходят через среду без необходимости ждать.

Когда вознаграждения возвращаются работниками ЦП, переходы могут быть вставлены в буфер воспроизведения. Награды за синтез кэшируются, чтобы избежать избыточных вычислений при повторном обнаружении состояния.

Результаты

Агенты RL учатся проектировать схемы tabula rasa исключительно посредством обучения с обратной связью по свойствам синтезированных схем. На рис. 5 показаны последние результаты*, в которых используются 64-разрядные сумматорные схемы, разработанные PrefixRL, сумматорные схемы с преобладанием Парето из современного инструмента EDA по площади и задержке.

Лучший сумматор PrefixRL достиг на 25% меньшей площади, чем сумматор инструмента EDA при той же задержке. Эти префиксные графы, отображающие оптимальные по Парето схемы суммирования после оптимизации физического синтеза, имеют неправильную структуру.

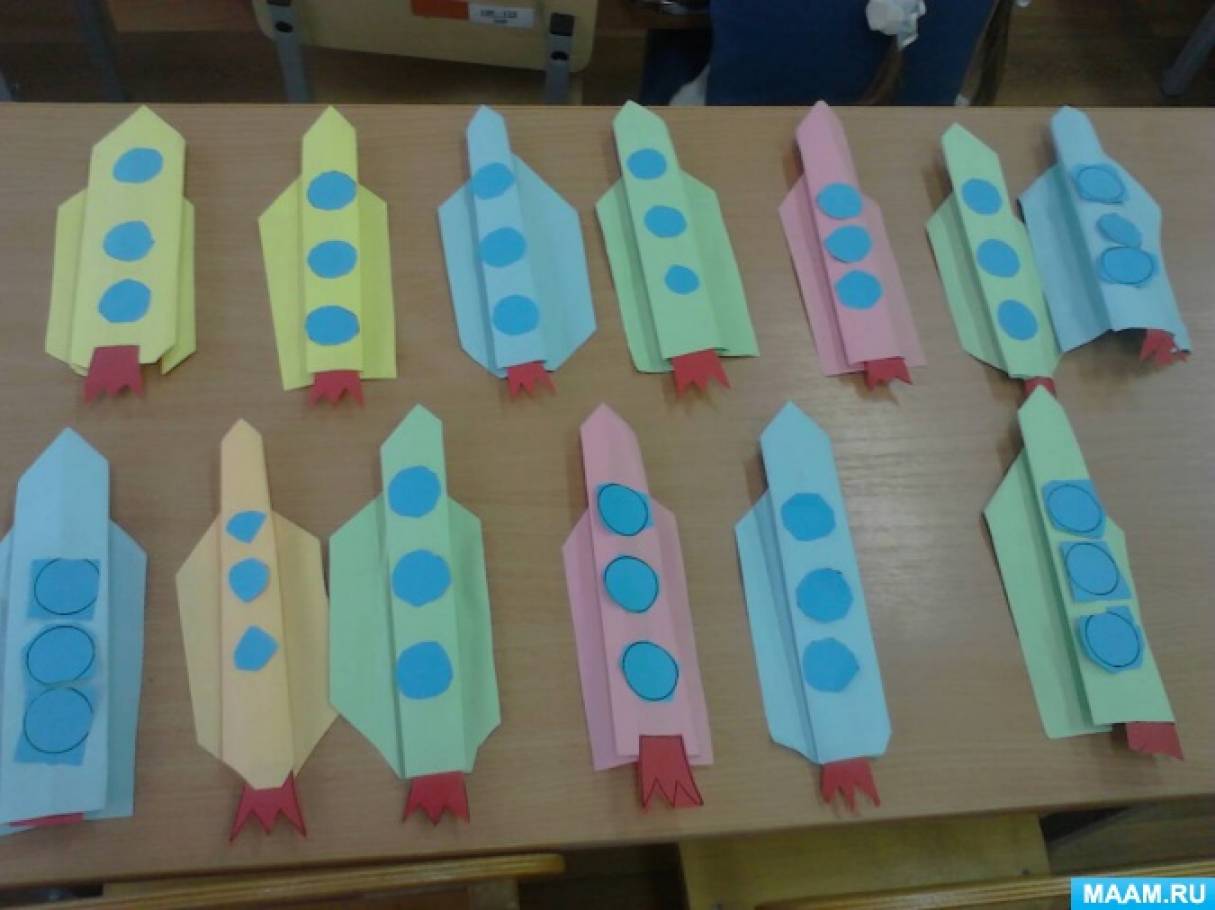

Учить детей приёму закручивания прямоугольника в цилиндр, круга в конус.

Учить детей приёму закручивания прямоугольника в цилиндр, круга в конус.

Помогите!

Помогите! Обратный отсчёт: 3, 2, 1 – Старт!

Обратный отсчёт: 3, 2, 1 – Старт! К корпусу прикрепляем шлюзы – треугольники, и иллюминаторы – кружки.

К корпусу прикрепляем шлюзы – треугольники, и иллюминаторы – кружки. Аплодисменты!

Аплодисменты!

Тело её покрыто густой рыжеё шерстью. У лисы роскошный пушистый хвост. У неё короткие ноги и острая мордочка. Глазки у лисы бусинками и светятся хитрым огнём.

Тело её покрыто густой рыжеё шерстью. У лисы роскошный пушистый хвост. У неё короткие ноги и острая мордочка. Глазки у лисы бусинками и светятся хитрым огнём.

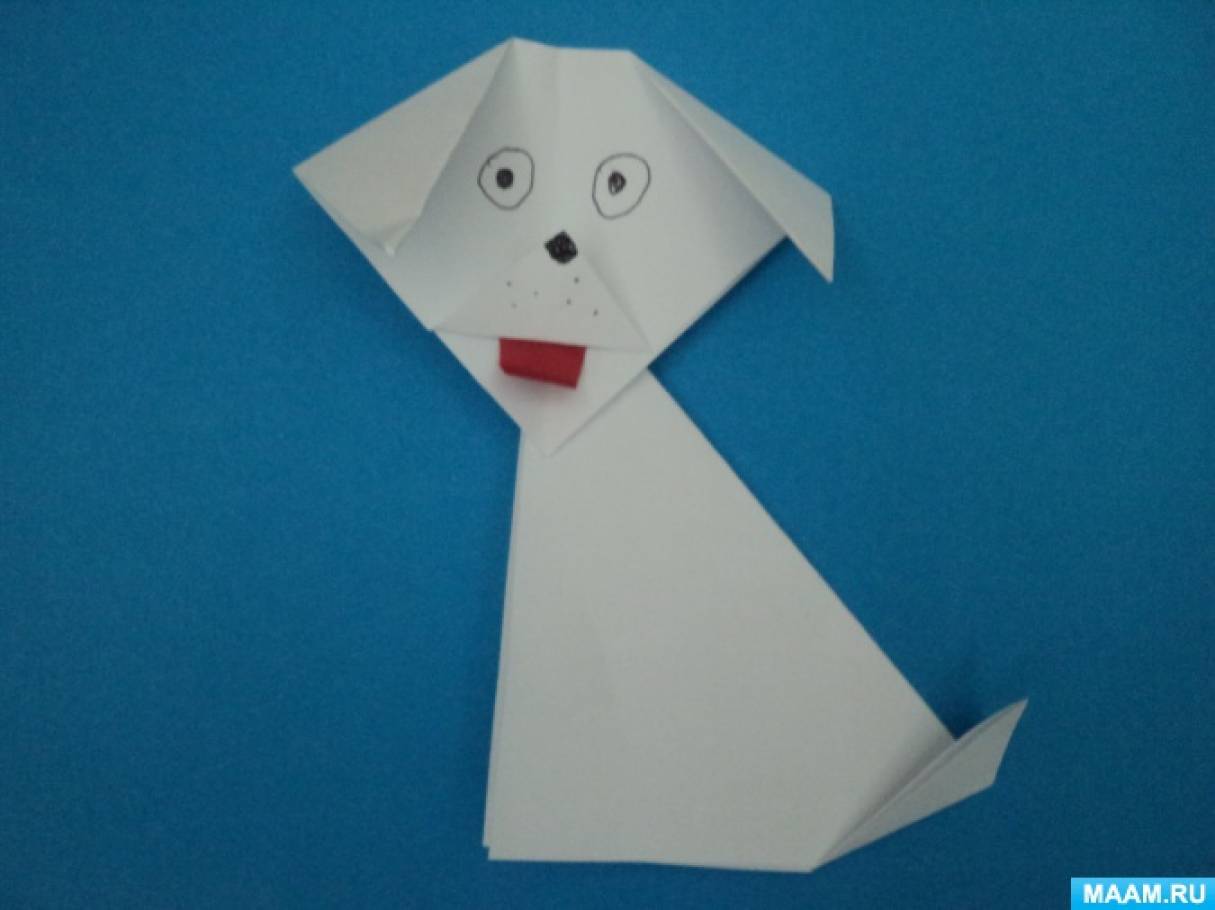

) – Правильно, конечно же не хватает носика и глаз. Для этого мы нарисуем их с помощьючёрного карандаша.

) – Правильно, конечно же не хватает носика и глаз. Для этого мы нарисуем их с помощьючёрного карандаша. Закреплять правила безопасности при работе с ножницами.

Закреплять правила безопасности при работе с ножницами.

Приложение к книге «Дошкольный логопункт. Документация, планирование и организация работы»

Приложение к книге «Дошкольный логопункт. Документация, планирование и организация работы» — Давайте накормим Машу нашим обедом. Что мы для этого возьмем? (Тарелка глубокая, мелкая тарелка, вилка, ложка) Посуда, из которой мы едим называется столовой, а с помощью чего – столовыми приборами. — Ну и после обеда Машу можно напоить вкусным чаем. Возьмите ту посуду, которая нам для этого понадобится (чайник, блюдце, чашка, чайная ложка). Она называется чайной.

— Давайте накормим Машу нашим обедом. Что мы для этого возьмем? (Тарелка глубокая, мелкая тарелка, вилка, ложка) Посуда, из которой мы едим называется столовой, а с помощью чего – столовыми приборами. — Ну и после обеда Машу можно напоить вкусным чаем. Возьмите ту посуду, которая нам для этого понадобится (чайник, блюдце, чашка, чайная ложка). Она называется чайной. Занятие «Собери осколки»

Занятие «Собери осколки» Тема: «Животные».

Тема: «Животные».